# Microenergie e ICT: Energy Aware Computation

Igor Neri - A pranzo con la Fisica Perugia, 29/11/2012

## Motivation

Energy-aware design, sometimes called energy-efficient design, is the design of a system to meet a given performance constraint with the minimum energy consumption.

- Critical in **battery-operated** devices.

- Critical in terms of **cost** (computer centers).

- Critical since energy is converted into heat.

- Algorithm: scheduling, power-down strategies

- Data management: memory-aware software optimization, routing protocol

- Architecture: instruction set selection, dynamic voltage and frequency scaling

- Virtualization: power saving of corporate data centers

- Circuit: device sizing, exploiting of transistor stacking to reduce leakage power

- Algorithm: scheduling, **power-down strategies**

- Data management: memory-aware software optimization, routing protocol

- Architecture: instruction set selection, dynamic voltage and frequency scaling

- Virtualization: power saving of corporate data centers

- Circuit: device sizing, exploiting of transistor stacking to reduce leakage power

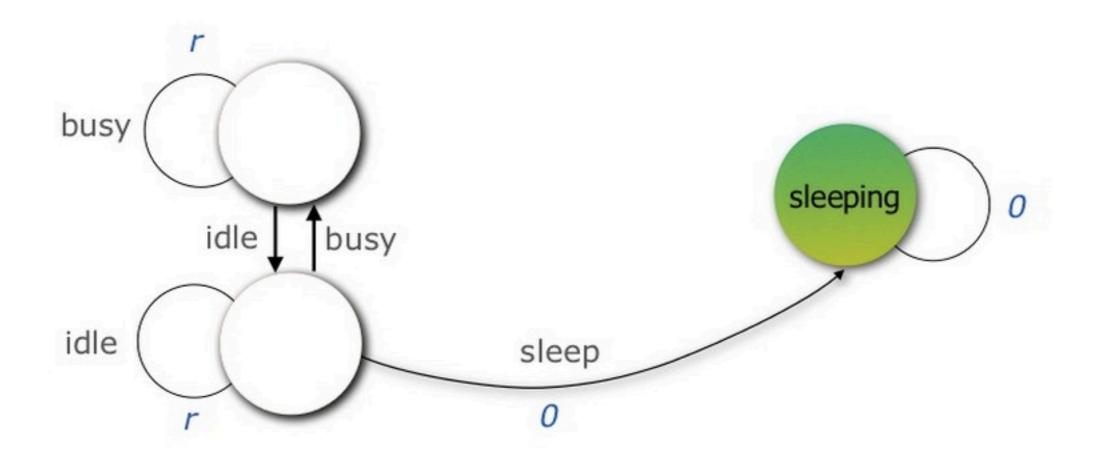

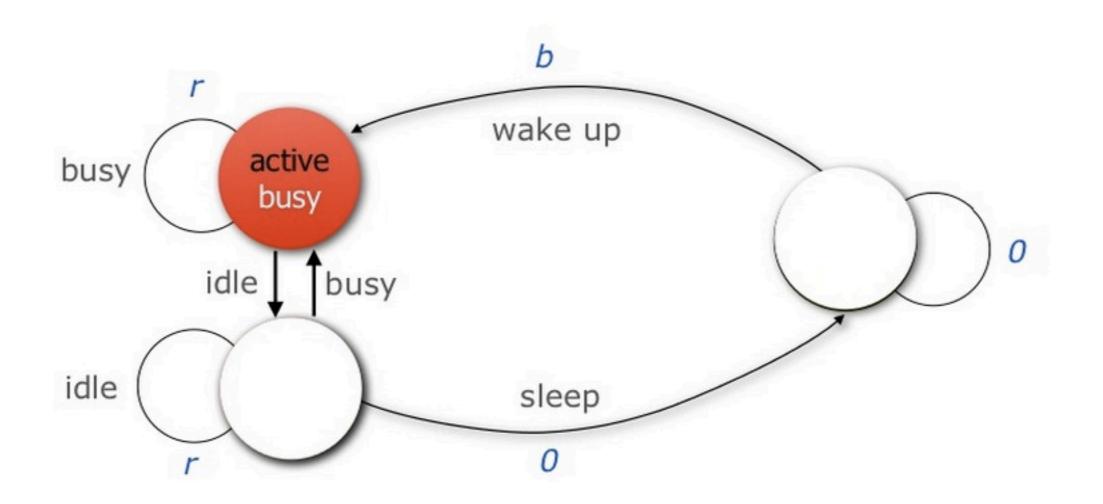

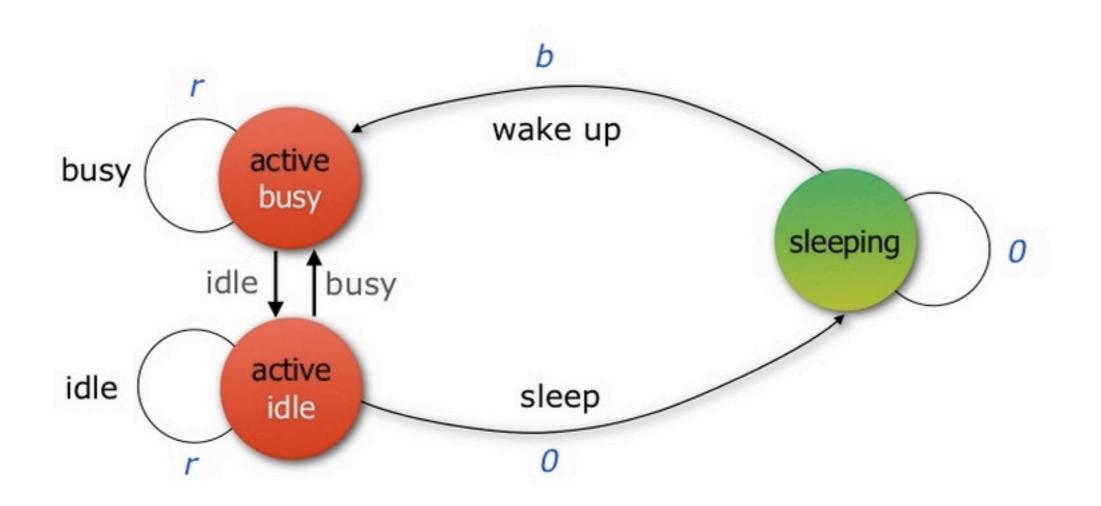

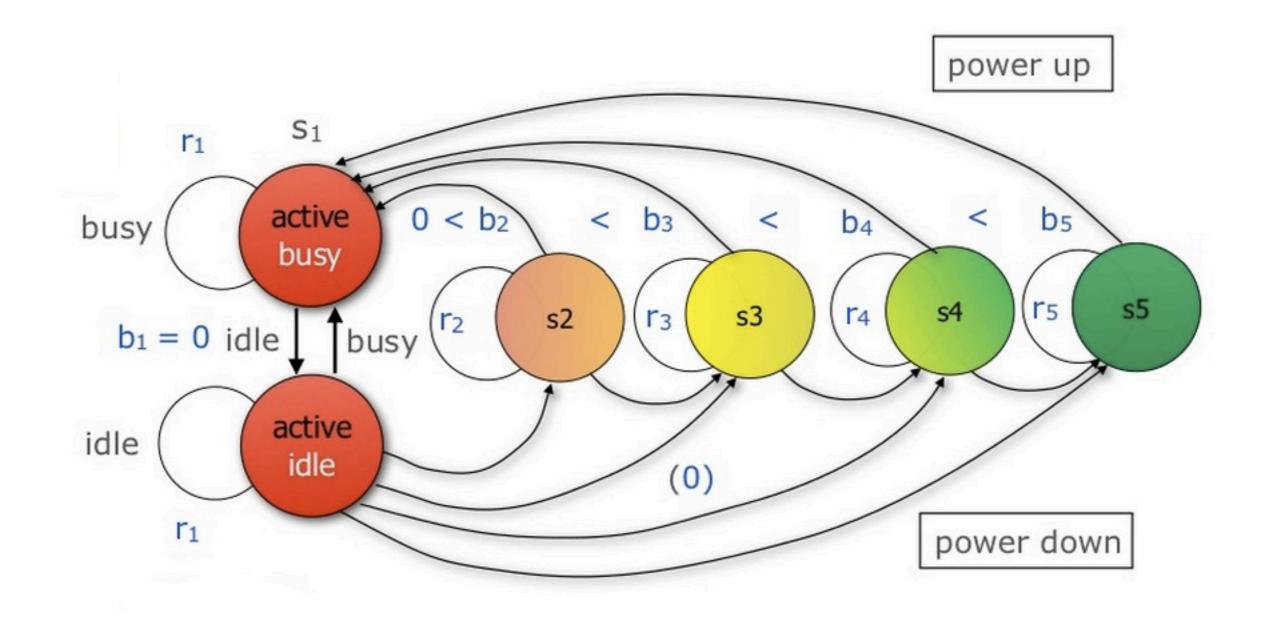

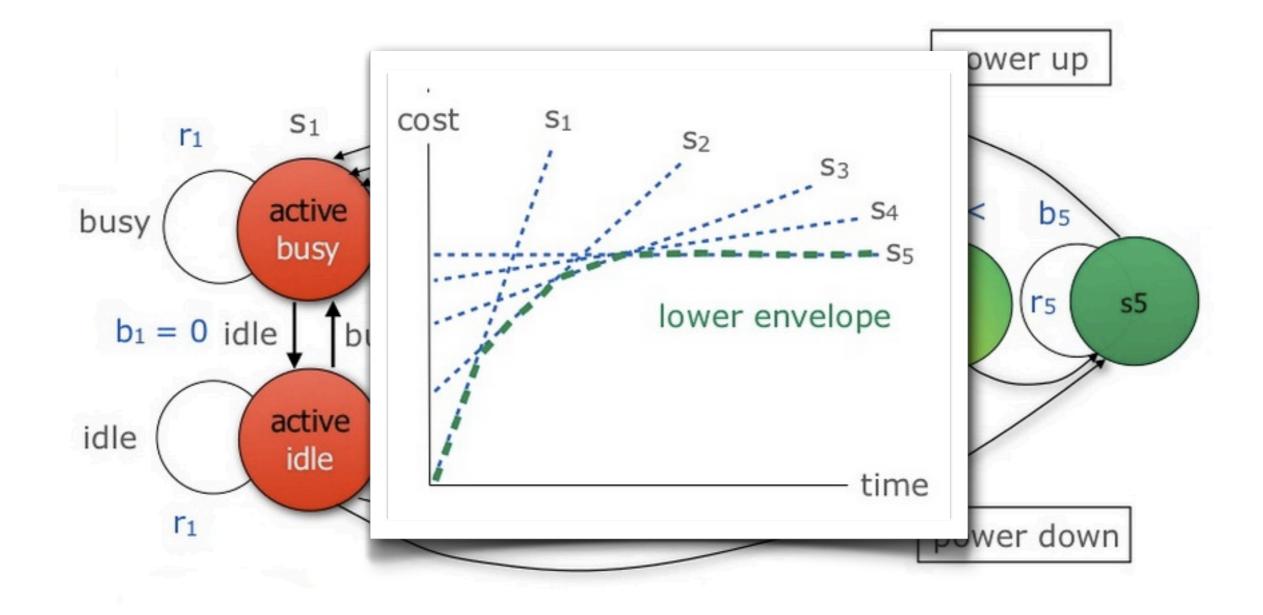

### Power down mechanism

A system in idle state can be transitioned to **low power modes**

The goal is to develop transition schedules minimizing energy consumption

**Power down mechanism:**

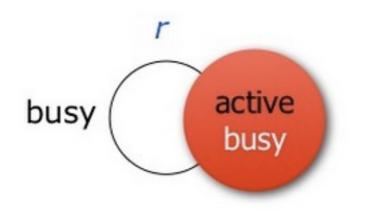

- Two states system

- Multiple states system

**Problem**: determine when to transition to the sleep state in order to minimize energy consumption.

### Power down mechanism: multiple states system

### Power down mechanism: multiple states system

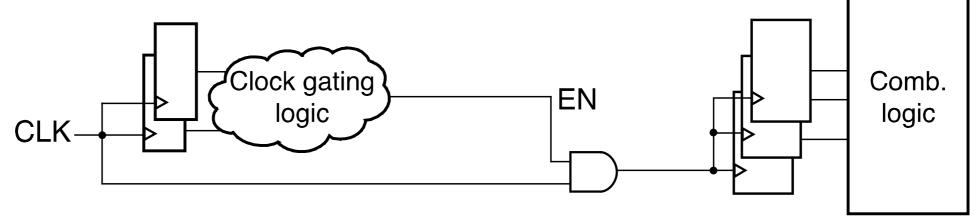

#### Circuits to reduce dynamic power

$$P_{\rm SW} = \frac{1}{2} \alpha C_{\rm L} V_{\rm dd}^2 f$$

- **P**<sub>sw</sub> average switch power consumption

- $\alpha$  probability of output switch

- CL load capacitance

- *f* clock frequency

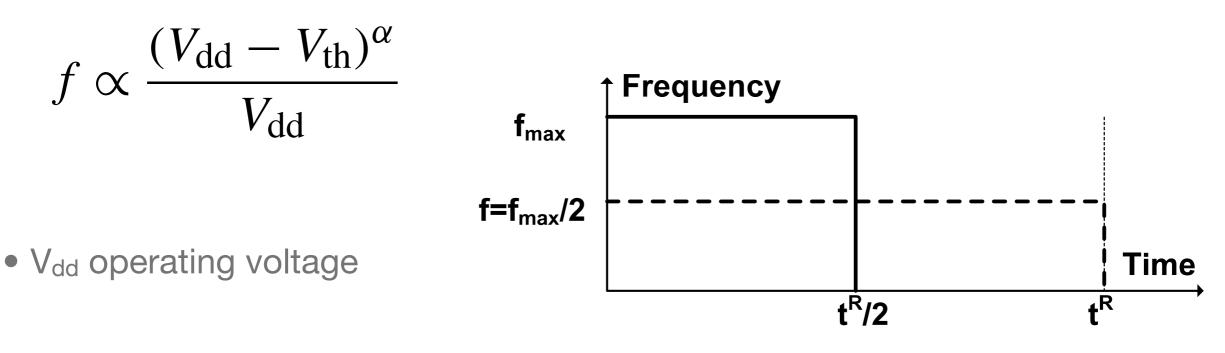

- V<sub>dd</sub> operating voltage

## Circuits to reduce dynamic power

Clock Gating

- Dual V<sub>dd</sub>: V<sub>ddh</sub> and V<sub>ddl</sub>

- V<sub>ddl</sub> used for gates that not affect the overall circuit speed

- Gate placement restricted (increase area and wire length)

- Level conversion

- Selection V<sub>ddl</sub>:V<sub>ddh</sub> is typically mandated by technology

- C.M. Kyung, S. Yoo Energy-Aware System Design

## Dynamic voltage and frequency scaling

- V<sub>th</sub> threshold voltage

- $\alpha$  is a measure of velocity saturation (1  $\leq \alpha \leq 2$ )

$$P_{\rm dyn} \propto f^3$$

C.M. Kyung, S. Yoo - Energy-Aware System Design

## Open problems & Hot topics

- Establishing metrics for assessing the energy efficiency of algorithms

- Estimation of the overhead caused by use of energy-aware algorithm

- Data aware computation

- Design of sub Landauer-limit logic gate and architecture

- Design of noise tolerant algorithms

# Thank you!